Product Summary

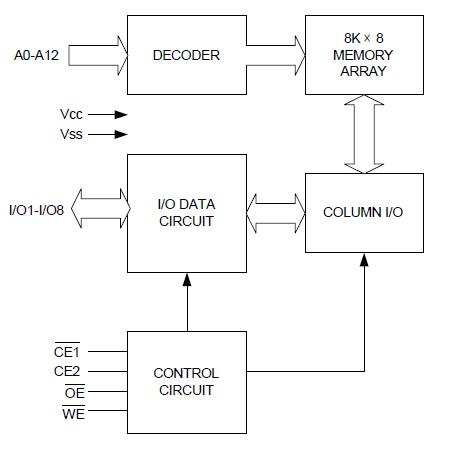

The UT6264CSC-70LL is a 65,536-bit low power CMOS static random access memory organized as 8,192 words by 8 bits. It is fabricated using high performance, high reliability CMOS technology. Easy memory expansion is provided by using two chip enable input.(CE1 ,CE2) ,and supports low data retention voltage for battery back-up operation with low data retention current. The UT6264CSC-70LL operates from a single 4.5V to 5.5V power supply and all inputs and outputs are fully TTL compatible.

Parametrics

UT6264CSC-70LL absolute maximum ratings: (1)Terminal Voltage with Respect to VSS, VTERM: -0.5 to +7.0 V; (2)Operating Temperature Commercial, TA: 0 to +70 ℃; (3)Storage Temperature, TSTG: -65 to +150℃; (4)Power Dissipation, PD: 1 W; (5)DC Output Current, IOUT: 50 mA; (6)Soldering Temperature (under 10 sec), Tsolder: 260℃.

Features

UT6264CSC-70LL features: (1)Access time: 35/70ns (max.); (2)Low power consumption: Operating: 45/30 mA (typ.); CMOS Standby : 2mA (typ.) normal, 2 μA (typ.) L-version; 1 μA (typ.) LL-version; (3)Single 4.5V to 5.5V power supply; (4)Operating temperature:; (5)Commercial: 0℃ to 70℃; (6)All inputs and outputs TTL compatible; (7)Fully static operation; (8)Three state outputs; (9)Data retention voltage: 2V (min.); (10)Package: 28-pin 600 mil PDIP; 28-pin 330 mil SOP.

Diagrams

|

UT621024 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UT6264B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UT6264C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UT6264CPC-35 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UT62L1024 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UT62L1024SC-70L |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)